Aspiring engineers who are preparing for the Graduate Aptitude Test in Engineering (GATE) understand the significance of thorough preparation and comprehensive study resources.

Through a meticulous examination of previous years’ question papers, we aim to provide you with valuable insights, key trends, and effective strategies to excel in Digital Electronics for your GATE exam.

GATE EE Syllabus for the Subject Digital Electronics

single stage active filters, Active Filters: Sallen Key, Butterworth, VCOs and timers,

Combinatorial and sequential logic circuits, multiplexers, demultiplexers,

Schmitt triggers, sample and hold circuits, A/D and D/A converters.

Analysis of Previous GATE Papers for Digital Electronics

| Year | Percentage of Marks |

|---|---|

| 2023 | 4% |

| 2022 | 2 % |

| 2021 | 6 % |

| 2020 | 3 % |

| 2019 | 4 % |

| 2018 | 7 % |

| 2017 | 4% |

| 2016 | 6% |

| 2015 | 4 % |

| 2014 | 7 % |

| 2013 | 2 % |

Recent GATE Paper Questions of Digital Electronics

The following questions have been asked from Digital Electronics, in GATE-EE 2023 Paper.

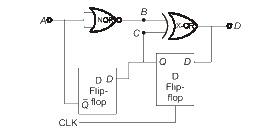

Q. Neglecting the delays due to the logic gates in the Circuit shown in figure, the decimal equivalent of the binary sequence [ABCD] of initial logic states, which will not change with clock, is ______.

Q. 2 In a given 8-bit general purpose micro-controller there are following flags. C-Carry, A-Auxiliary Carry, 0-0verfIow flag. P-Parity (O for even, 1 for Odd) RO and RI are the two general purpose registers of the micro-controller. After execution Of the following instructions, the decimal equivalent of the binary sequence of the flag pattern [CAOP] will be ______.

MOV R0, +0x60

MOV RI, +0x46

ADD R0, RI

GATE Paper Solutions for Digital Electronics

Last 25+ years GATE Papers with Authentic Solutions